製品・技術情報

KVASER CANプロトコルとは?(CANプロトコルチュートリアル)

- 2022.02.22

PART 7:CANビットタイミング

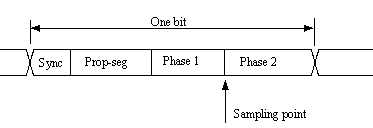

ビットレイアウト

CAN busの各ビットは、タイミング目的のために少なくとも4 quantaに分割されます。quantaは、論理的に4つのグループまたはセグメントに分割されます。

- 同期セグメント

- 伝播セグメント

- フェーズセグメント 1

- フェーズセグメント 2

これはCANデータビットの画像です:

同期セグメントは、常に1 quantum長でクロックの同期に使用されます。バス上でデータが変化したとき、ここでビットエッジが発生することが予想されます。

フェーズセグメントは、クロックを同期させるために必要に応じて短縮(フェーズセグメント1)または延長(フェーズセグメント2)することができます。

バスレベルは、フェーズセグメント1とフェーズセグメント2の間の境界でサンプリングされます。

ほとんどのCANコントローラは、1ビットの間に3回サンプリングするオプションを提供しています。この場合、サンプリングは、 サンプリングポイントの前の2つのquantaの境界で行われ、結果は多数決デコードの対象となります(少なくとも82527の場合は、これが当てはまります)。

クロック同期

on-chipバスクロックを調整するためにCANコントローラは、quantaの整数によってビットの長さを短縮または延長することがあります。これらのビットタイム調整の最大値は、SJW(Synchronization Jump Width)と呼ばれます。

ハード同期は、スタートビットのレセッシブ-to-ドミナント(recessive-to-dominant)の移行で発生します。ビットタイムは、そのエッジから再スタートされます。

再同期は、メッセージ内の同期セグメント内でビットエッジが発生しない場合に発生します。フェーズセグメントの1つは、信号の位相誤差に依存する量で短縮または延長されます。使用できる最大量は、Synchronization Jump Widthパラメータによって決まります。

ビットタイミングレジスタ計算

ほとんどのCANコントローラでは、プログラマが以下のパラメータを使用してビットタイミングを設定することができます:

- クロックプリスケーラ値

- サンプリングポイントの前のquantaの数

- サンプリングポイントの後のquantaの数

- SJW(Synchronization Jump Width)のquantaの数

通常、この目的のために2つのレジスタが用意されています:btr0とbtr1です。ただし、コントローラによって若干の違いがありますのでデータシートをよく読んでください。

NXP(旧Philips)の82c200とSJA1000では、レジスタのレイアウトは次のようになっています。

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

|---|---|---|---|---|---|---|---|---|

| btr0 | sjw1 | sjw0 | BRP5 | BRP4 | BRP3 | BRP2 | BRP1 | BRP0 |

| btr1 | SAM | TSEG22 | TSEG21 | TSEG20 | TSEG13 | TSEG12 | TSEG11 | TSEG10 |

- BRP0~BRP5は、クロックプリスケーラ値を設定します。

- SJW0~SJW1は、SJWの長さを設定します。

- TSEG10~TSEG13は、サンプリングポイントの前のquantaの数を設定します(スタートビットは含まれません)。

- TSEG20~TSEG22は、サンプリングポイントの後のquantaの数を設定します。

- SAMは、3つのサンプルを取得する場合は1、1つのサンプルで十分な場合は0に設定されます。

Note:これらのパラメータの実際の値は、レジスタに書き込まれた値より1つ多くなります。

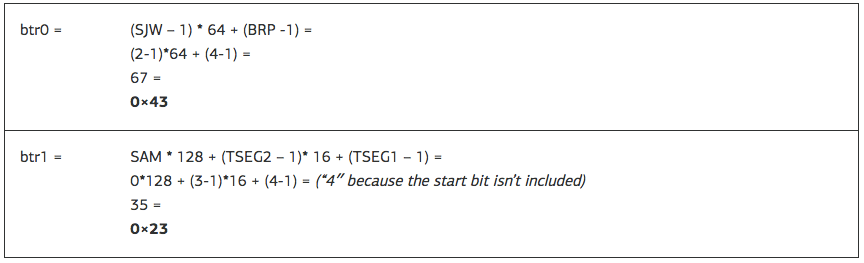

例: SJA1000に送られるオシレータ信号が16 MHzでビットレートが250 kbit/sの場合、サンプリングポイントは、ビット全体の62%に近い値、SJWは2 quantaで、次の値を設定できます:

BRP = 4、これは2 * 4/16000000 s = 500 nsのquantum長を与え、そして

TSEG1 = 5、これはサンプリングポイントの前に 5 quantumを与え、そして

TSEG2 = 3、これはサンプリングポイントの後に3 quantumを与えます。

各ビットは、5 + 3 = 8 quantaで構成され、1/(8 * 500 ns) = 250 kbit/sの所望のビットレートになります。レジスタ値は、ここの例に示すようにします。

サンプリングポイントは、ビットの5/8 = 62.5%です